## EE 330 Lecture 16

## Devices in Semiconductor Processes

- Diodes (continued)

- Capacitors

- MOSFETs

#### IOWA STATE UNIVERSITY

OF SCIENCE AND TECHNOLOGY

Office of the Senior Vice President and Provost 1550 Beardshear Hall Ames, IA 50011-2021 Phone 515 294-0070 FAX 515 294-8844

Southert Andree Weels

Interoffice Communication

Date: September 29, 2021

To: Iowa State University Faculty

From: Jonathan Wickert

Senior Vice President and Provost

Andrea Wheeler

President, Faculty Senate

Subject: Public Health Messaging for Students via Canvas

Iowa State University's public health team is launching a series of weekly messages to encourage students to get vaccinated and wear a mask as well as inform them about the spread of COVID-19 on campus and in the community.

Similar to the Cyclones Care campaign, the messages were developed with input from the Faculty Senate Executive Board, and in particular Meghan Gillette, who has expertise in communication with college-age adults. The messages will be posted on Canvas every Wednesday morning, following the weekly update to the COVID-19: By the numbers website, and will remain on the site for 24 hours. The messages will be displayed on the faculty dashboard in Canvas, so you can access them easily.

We encourage you to share this information with students during class or as part of routine messages and communications with students. The Canvas messages will include a link to the COVID-19: By the numbers website, if you would like to pull the weekly data to share.

We ask that department chairs share this memo with all instructors, including graduate student instructors, and teaching assistants, and academic advisors and staff engaged in instruction and student success.

Thank you for your work this semester and help in keeping our students informed.

C: Wendy Wintersteen, President

Pam Cain, Senior Vice President for Operations and Finance

Toyia Younger, Senior Vice President for Student Affairs

Provost's Council

Chris Johnsen, President, Professional and Scientific Council

As a courtesy to fellow classmates, TAs, and the instructor

Wearing of masks during lectures and in the laboratories for this course would be appreciated irrespective of vaccination status

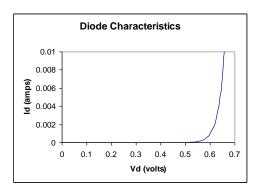

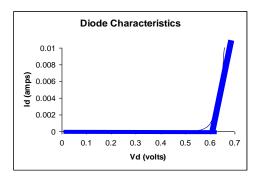

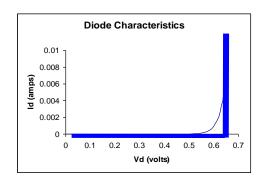

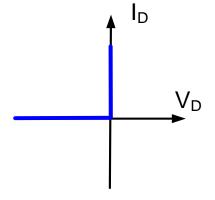

## **Diode Models**

Which model should be used?

The simplest model that will give acceptable results in the analysis of a circuit

# Use of Piecewise Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

#### Observations:

- Analysis generally simplified dramatically (particularly if piecewise model is linear)

- Approach applicable to wide variety of nonlinear devices

- Closed-form solutions give insight into performance of circuit

- Usually much faster than solving the nonlinear circuit directly

- Wrong guesses in the state of the device do not compromise solution (verification will fail)

- Helps to guess right the first time

- Detailed model is often not necessary with most nonlinear devices

- Particularly useful if piecewise model is PWL (but not necessary)

- For <u>practical</u> circuits, the simplified approach usually applies

**Key Concept For Analyzing Circuits with Nonlinear Devices**

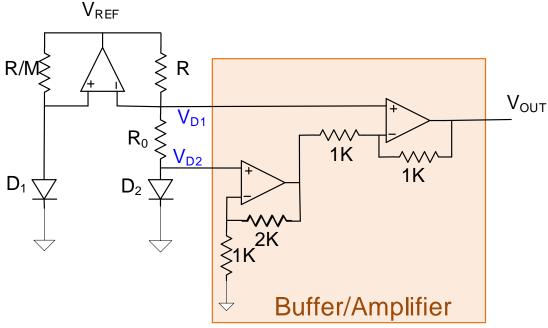

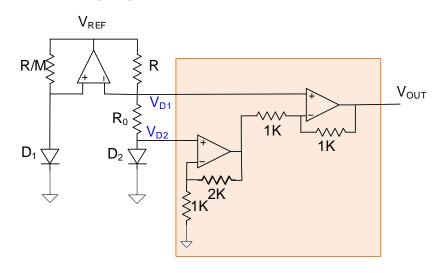

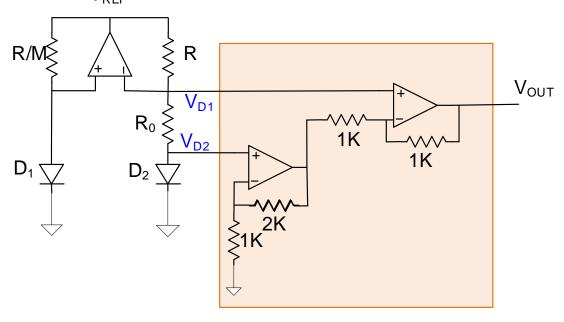

# A Diode Application

May need compensation and startup circuits

For appropriate R<sub>0</sub>, serves as bandgap voltage reference (buffer/amplifier excluded)

$$V_{REF} = V_{D1} + \frac{R}{R_0} (V_{D1} - V_{D2})$$

If buffer/amplifier added, serves as temperature sensor at V<sub>OUT</sub>

$$V_{OUT} = 2(V_{D2} - V_{D1})$$

# A Diode Application

$$V_{\text{OUT}} = 2(V_{\text{D2}} - V_{\text{D1}})$$

Analysis of temperature sensor (assume D<sub>1</sub> and D<sub>2</sub> matched)

$$I_{D2}(T) = \left(J_{SX}\left[T^{m}e^{\frac{-V_{G0}}{V_{t}}}\right]\right)Ae^{\frac{V_{D2}}{V_{t}}}$$

$$I_{D1}(T) = \left(J_{SX}\left[T^{m}e^{\frac{-V_{G0}}{V_{t}}}\right]\right)Ae^{\frac{V_{D1}}{V_{t}}}$$

$$I_{D2}(T) = MI_{D1}(T)$$

$$V_{t} = \frac{k}{a}T$$

$$\qquad \qquad \left( \mathbf{J}_{\mathrm{SX}} \left[ \mathbf{T}^{\mathrm{m}} \mathbf{e}^{\frac{-\mathbf{V}_{\mathrm{GO}}}{\mathbf{V}_{\mathrm{t}}}} \right] \right) \mathbf{A} \mathbf{e}^{\frac{\mathbf{V}_{\mathrm{D2}}}{\mathbf{V}_{\mathrm{t}}}} = M \left( \mathbf{J}_{\mathrm{SX}} \left[ \mathbf{T}^{\mathrm{m}} \mathbf{e}^{\frac{-\mathbf{V}_{\mathrm{GO}}}{\mathbf{V}_{\mathrm{t}}}} \right] \right) \mathbf{A} \mathbf{e}^{\frac{\mathbf{V}_{\mathrm{D1}}}{\mathbf{V}_{\mathrm{t}}}}$$

Cancelling terms and taking In we obtain

$$V_{D2} - V_{D1} = V_{t} \ln M$$

Thus

$$V_{OUT} = 2(V_{D2} - V_{D1}) = 2 \ln M \cdot \frac{k}{q} T$$

# A Diode Application

May need compensation and startup circuits

For appropriate R<sub>0</sub>, serves as bandgap voltage reference

$$V_{REF} = V_{D1} + \frac{R}{R_0} (V_{D1} - V_{D2})$$

If buffer/amplifier added, serves as temperature sensor at  $V_{\text{OUT}}$

$$V_{OUT} = 2(V_{D2} - V_{D1})$$

Analysis of  $V_{REF}$  to show output is nearly independent of T and  $V_{DD}$  is more tedious

## Use of <u>Piecewise</u> Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

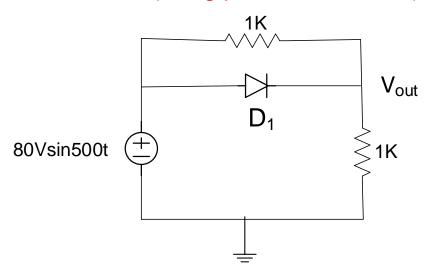

What about nonlinear circuits (using piecewise models) with time-varying inputs?

Same process except state verification (step 3) may include a range where solution is valid

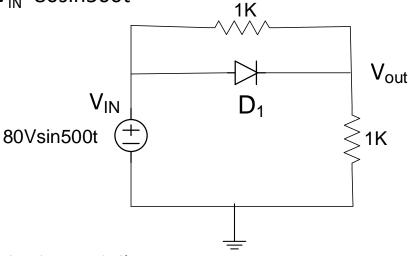

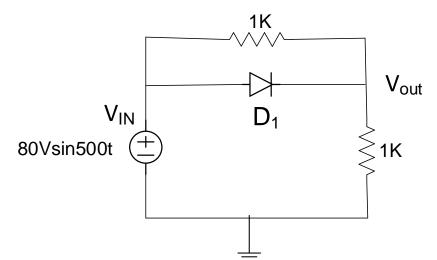

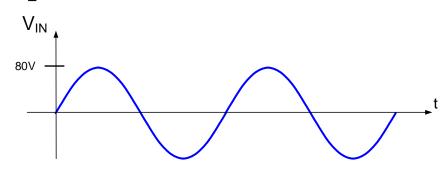

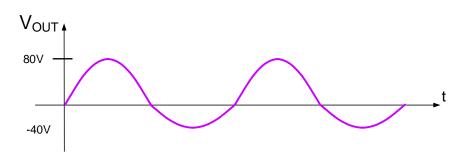

Example: Determine  $V_{OUT}$  for  $V_{IN}$ =80sin500t

Guess D<sub>1</sub> ON (will use ideal diode model)

$V_{OUT}=V_{IN}=80\sin(500t)$

Valid for

$$I_D > 0$$

$I_D = \frac{V_{IN}}{1K}$

Thus valid for  $V_{IN} > 0$

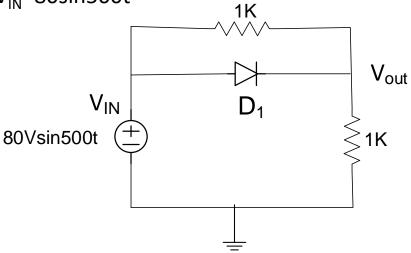

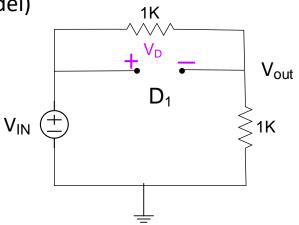

Example: Determine  $V_{OUT}$  for  $V_{IN}$ =80sin500t

Guess D<sub>1</sub> OFF (will use ideal diode model)

$$V_{OUT} = V_{IN}/2 = 40 sin(500t)$$

$$\text{Valid for V}_{\text{D}} \text{<0} \qquad V_{D} = \frac{V_{IN}}{2}$$

Thus valid for  $V_{IN} < 0$

#### Example: Determine V<sub>OUT</sub> for V<sub>IN</sub>=80sin500t

#### Thus overall solution

$$V_{OUT} = \begin{cases} 80\sin 500t & for V_{IN} > 0\\ 40\sin 500t & for V_{IN} < 0 \end{cases}$$

## Use of <u>Piecewise</u> Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

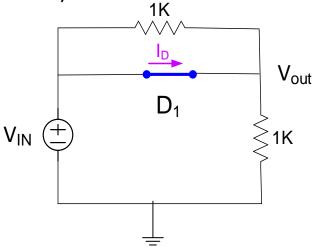

What about circuits (using piecewise models) with multiple nonlinear devices?

Guess state for each device (multiple combinations possible)

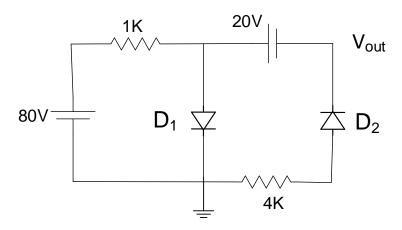

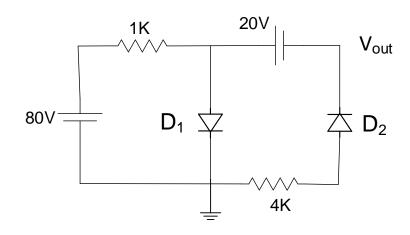

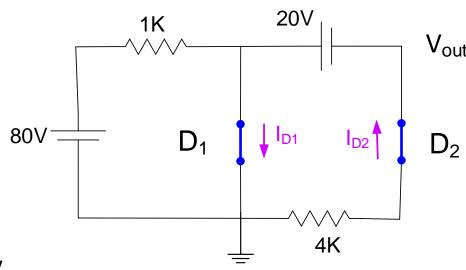

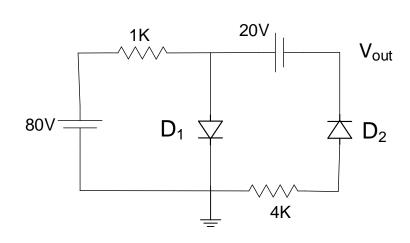

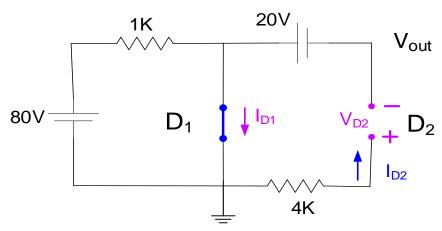

## Example: Obtain V<sub>OUT</sub>

### Example: Obtain V<sub>OUT</sub>

Guess D<sub>1</sub> and D<sub>2</sub> on

Valid for  $I_{D2}>0$  and  $I_{D1}>0$

$$I_{D2} = \frac{20V}{4K} = 5mA > 0$$

$I_{D1} = \frac{80V}{1K} + I_{D2} = 85mA > 0$

**Validates**

**Validates**

Since validates, solution is valid

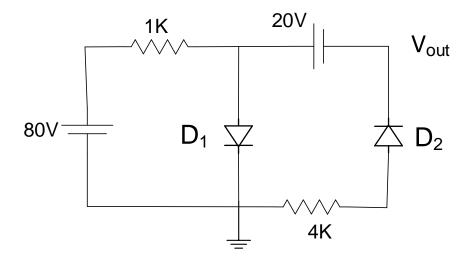

### Example: Obtain V<sub>OUT</sub>

If we had guessed wrong Guess D<sub>1</sub> ON and D<sub>2</sub> OFF

$$V_{OUT} = -20V$$

Valid for I<sub>D1</sub>>0 and

$$V_{D2} < 0$$

$$I_{D1} = \frac{80V}{1K} + I_{D2} = 80mA > 0$$

$$V_{D2} = +20$$

**Validates**

Fails Validation

Since fails to validate, solution is not valid so guess is wrong!

# Use of <u>Piecewise</u> Models for Nonlinear Devices when Analyzing Electronic Circuits

#### Single Nonlinear Device

#### Process:

- 1. Guess state of the device

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify model (if necessary)

#### Process:

### Multiple Nonlinear Devices

- 1. Guess state of each device (may be multiple combinations)

- 2. Analyze circuit

- 3. Verify State

- 4. Repeat steps 1 to 3 if verification fails

- 5. Verify models (if necessary)

Analytical solutions of circuits with multiple nonlinear devices are often impossible to obtain if detailed non-piecewise nonlinear models are used

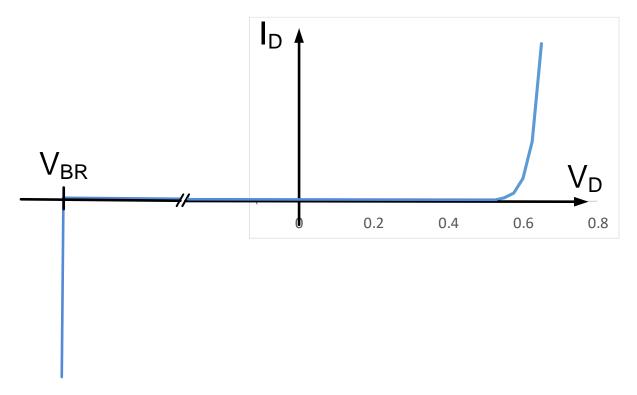

## Diode Breakdown

- Diodes will "break down" if a large reverse bias is applied

- Unless current is limited, reverse breakdown is destructive

- Breakdown is very sharp

- For many signal diodes, V<sub>BR</sub> is in the -100V to -1000V range

- Relatively easy to design circuits so that with correct diodes, breakdown will not occur

- Zener diodes have a relatively small breakdown and current is intentionally limited to use this breakdown to build voltage references

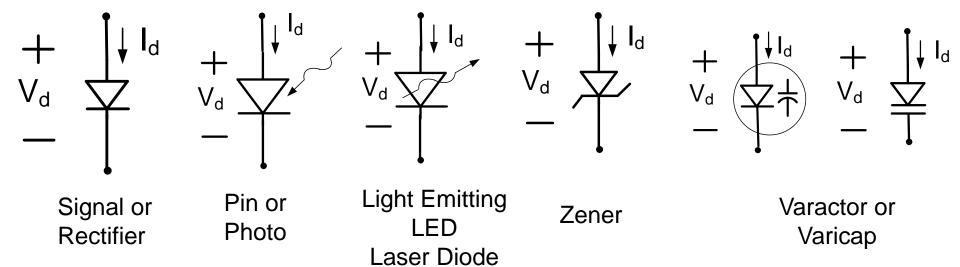

## Types of Diodes

#### pn junction diodes

#### **Metal-semiconductor junction diodes**

Schottky Barrier

## Basic Devices and Device Models

- Resistor

- Diode

- Capacitor

- MOSFET

- BJT

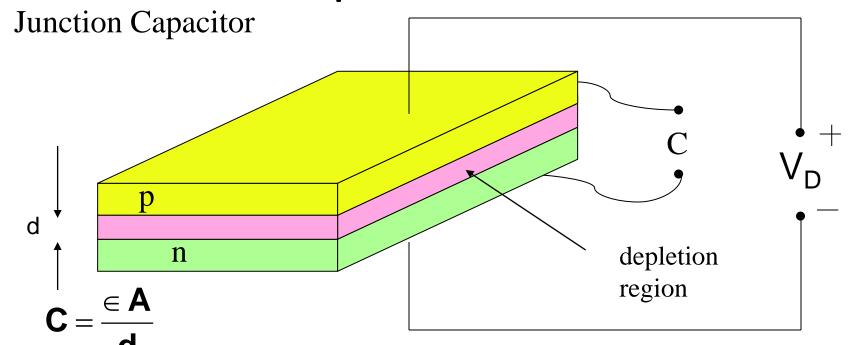

# Capacitors

- Types

- Parallel Plate

- Fringe

- Junction

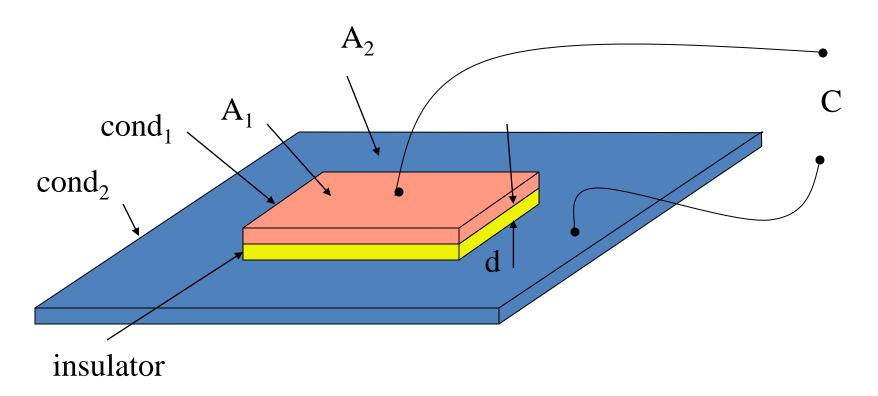

# Parallel Plate Capacitors

$A = area of intersection of A_1 & A_2$

One (top) plate intentionally sized smaller to determine C

$$C = \frac{\in A}{d}$$

# Parallel Plate Capacitors

If

$$C_d = \frac{Cap}{unit area}$$

$$\label{eq:continuity} \begin{split} \boldsymbol{C} &= \frac{\epsilon\,\boldsymbol{A}}{d} \\ \boldsymbol{C} &= \boldsymbol{C}_{d}\boldsymbol{A} \end{split}$$

$$C = C^{d}A$$

where

$$\mathbf{C_d} = \frac{\mathbf{\epsilon}}{\mathbf{d}}$$

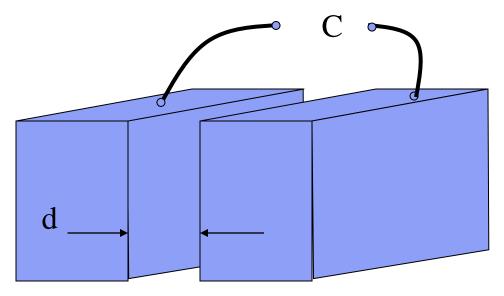

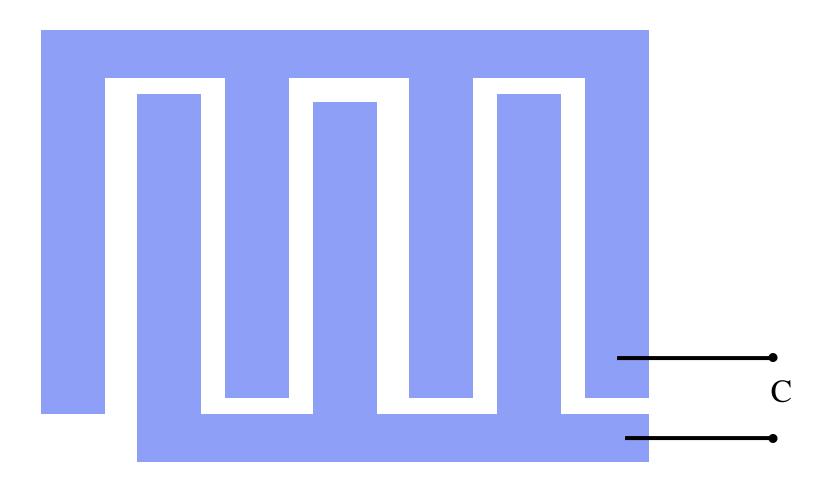

# **Fringe Capacitors**

$$\mathbf{C} = \frac{\mathbf{\epsilon} \, \mathbf{A}}{\mathsf{d}}$$

A is the area where the two plates are parallel Only a single layer is needed to make fringe capacitors

# Fringe Capacitors

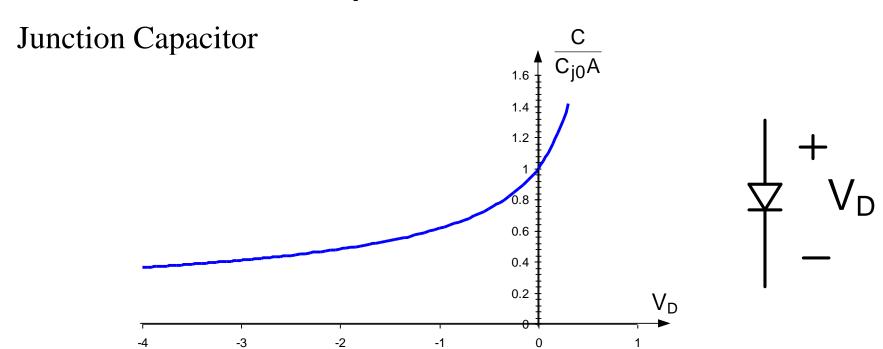

# Capacitance

**□** is dielectric constant

$$C = \frac{C_{jo}A}{\left(1 - \frac{V_D}{I}\right)^n} \qquad \text{for } V_{FB} < \frac{\phi_B}{2}$$

Note: d is voltage dependent

- -capacitance is voltage dependent

- -usually parasitic caps

- -varicaps or varactor diodes exploit voltage dep. of C

C<sub>j0</sub> is the zero—bias junction capacitance density

Model parameters  $\{C_{io}, n, \phi_B\}$  Design parameters  $\{A\}$

$$\phi_{\text{B}} \cong 0.6 \text{V}$$

$$m n \simeq 0.5$$

# Capacitance

$$C = \frac{C_{jo}A}{\left(1 - \frac{V_{D}}{\varphi_{D}}\right)^{n}} \qquad for \ V_{FB} < \frac{\varphi_{E}}{2}$$

Voltage dependence is substantial

$\phi_{\rm B} \simeq 0.6 \text{V} \quad \text{n} \simeq 0.5$

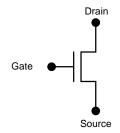

## Basic Devices and Device Models

- Resistor

- Diode

- Capacitor

BJT

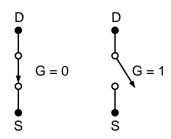

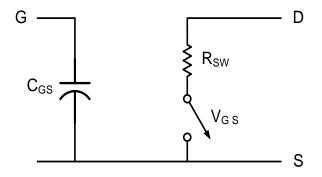

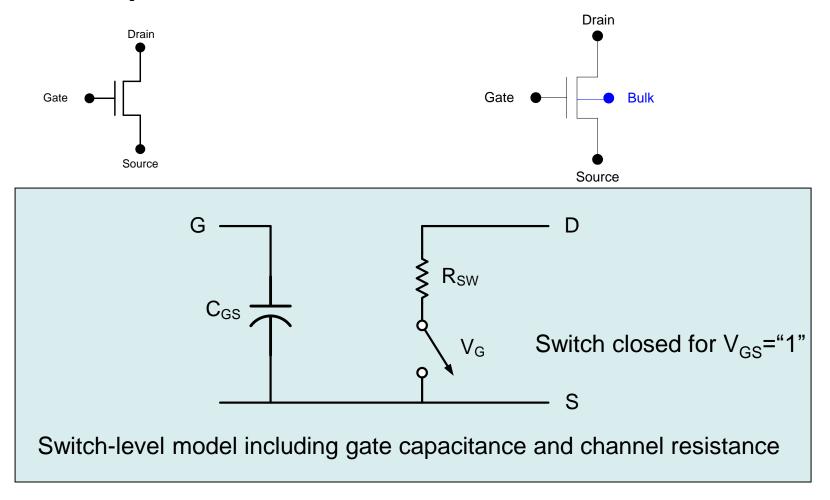

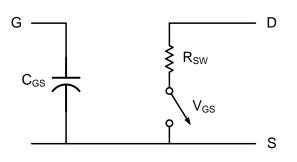

## Summary of Existing Models (for n-channel)

1. Switch-Level model

2. Improved switch-level model

Switch closed for  $|V_{GS}|$ = large Switch open for  $|V_{GS}|$ = small

# Improved Switch-Level Model

- Connect the gate capacitance to the source to create lumped model

- Still neglect bulk connection

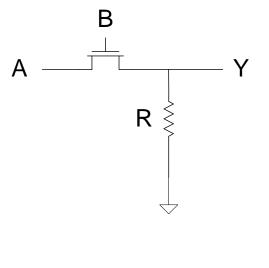

# Limitations of Existing MOSFET Models

For minimum-sized devices in a 0.5 $\mu$  process with  $V_{DD}$ =5V

$$C_{GS} \cong 1.5 fF$$

$$R_{sw} \cong \begin{array}{c} 2K\Omega & n-channel \\ 6K\Omega & p-channel \end{array}$$

What is Y when A=B=VDD

What is R<sub>SW</sub> if MOSFET is not minimum sized?

What is power dissipation if A is stuck at an intermediate voltage?

Better Model of MOSFET is Needed!

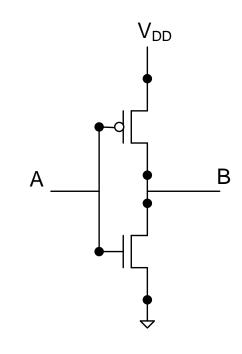

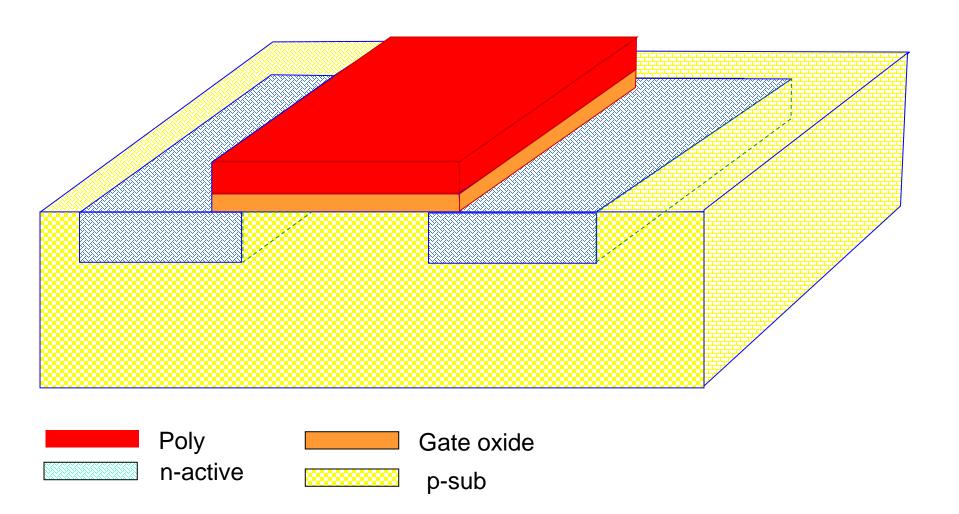

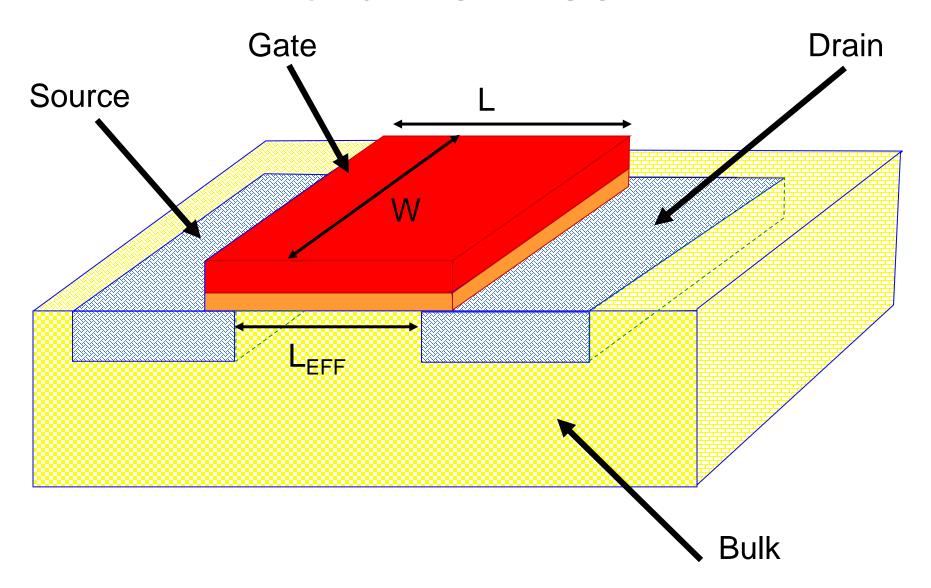

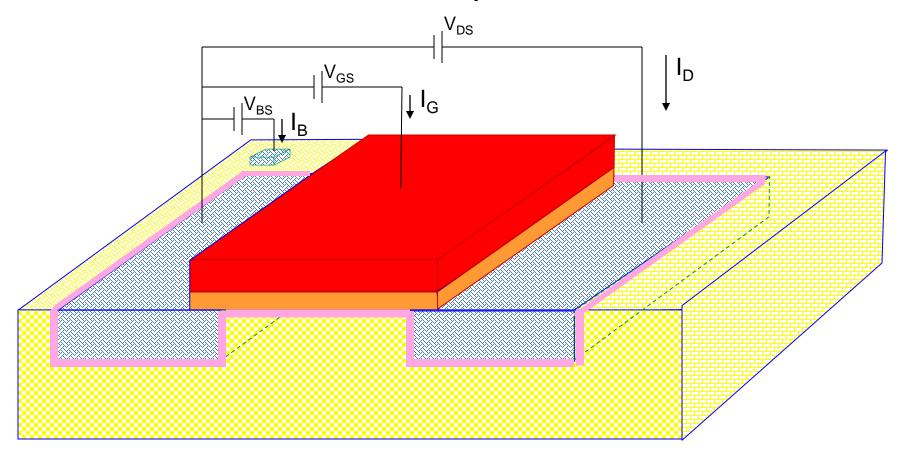

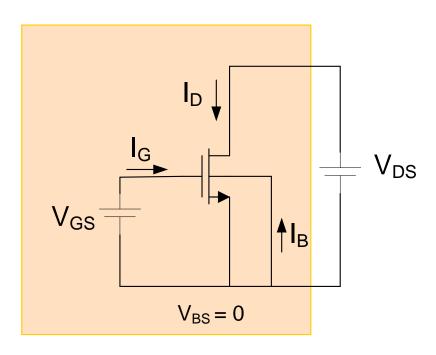

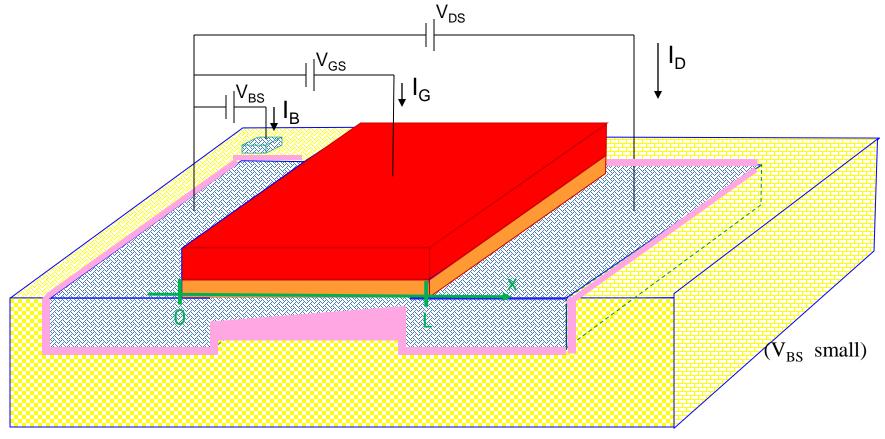

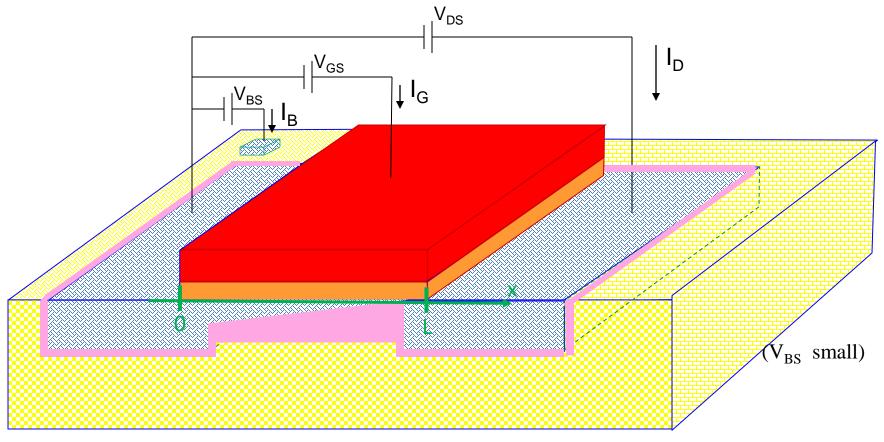

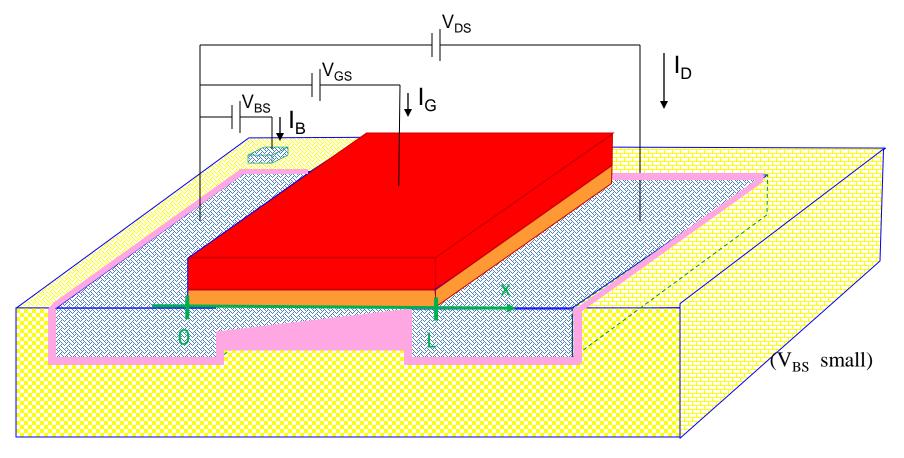

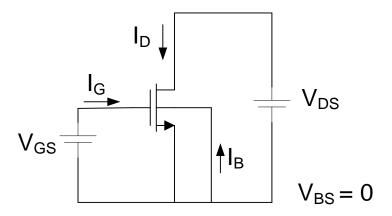

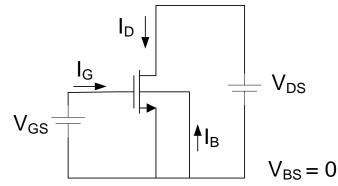

# n-Channel MOSFET

# n-Channel MOSFET

## n-Channel MOSFET

- In what follows assume all pn junctions reverse biased (almost always used this way)

- Extremely small reverse bias pn junction current can be neglected in most applications

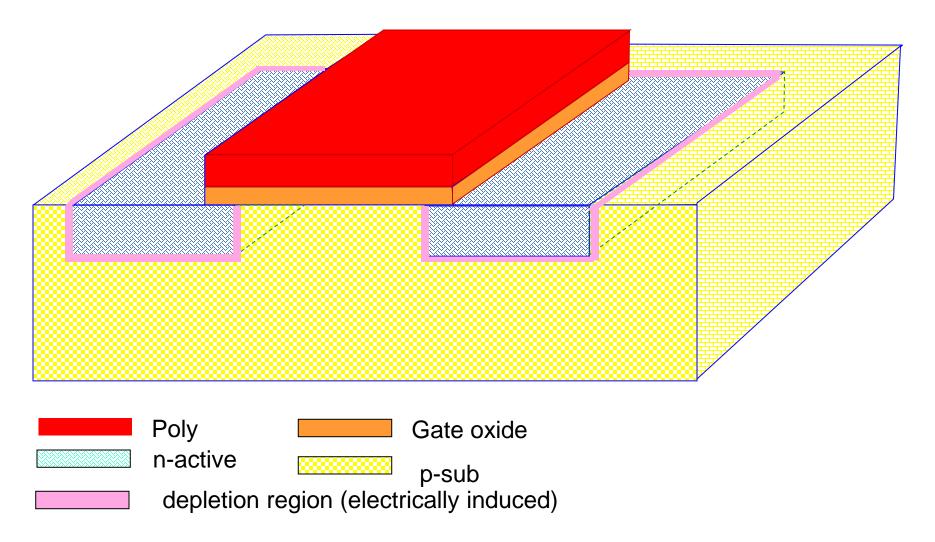

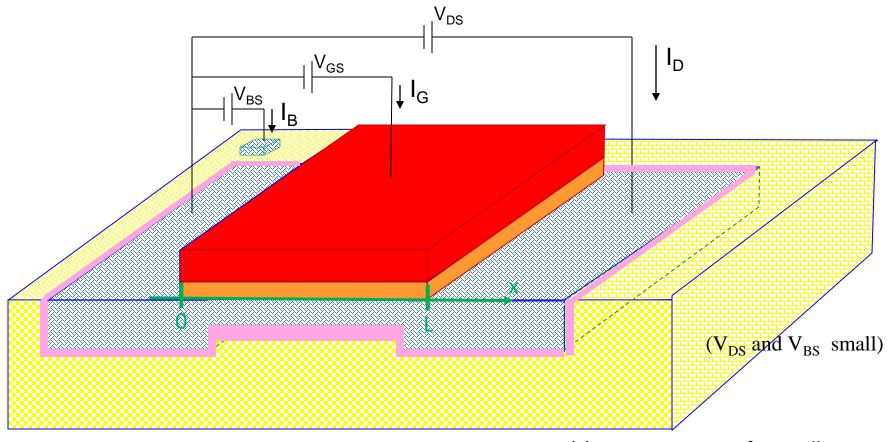

## n-Channel MOSFET Operation and Model

$\begin{array}{c} \text{Apply small $V_{GS}$} \\ \text{($V_{DS}$ and $V_{BS}$ assumed to be small)} \\ \text{Depletion region electrically induced in channel} \\ \text{Termed "cutoff" region of operation} \end{array}$

$$_{\rm D}=0$$

$_{\rm G}=0$

$_{\rm B}=0$

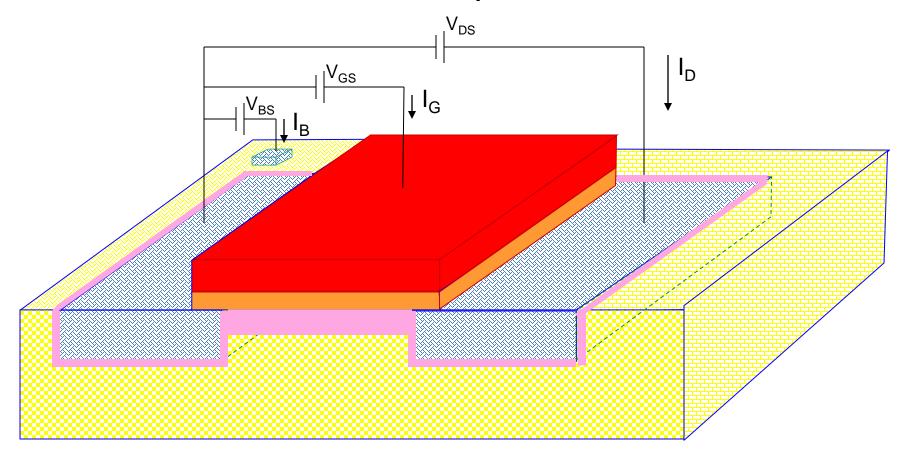

## n-Channel MOSFET Operation and Model

Increase  $V_{GS}$  ( $V_{DS}$  and  $V_{BS}$  assumed to be small)

Depletion region in channel becomes larger

$$I_D=0$$

$$I_G=0$$

$$I_B=0$$

$$I_{D}=0$$

$$I_{G}=0$$

$$I_{B}=0$$

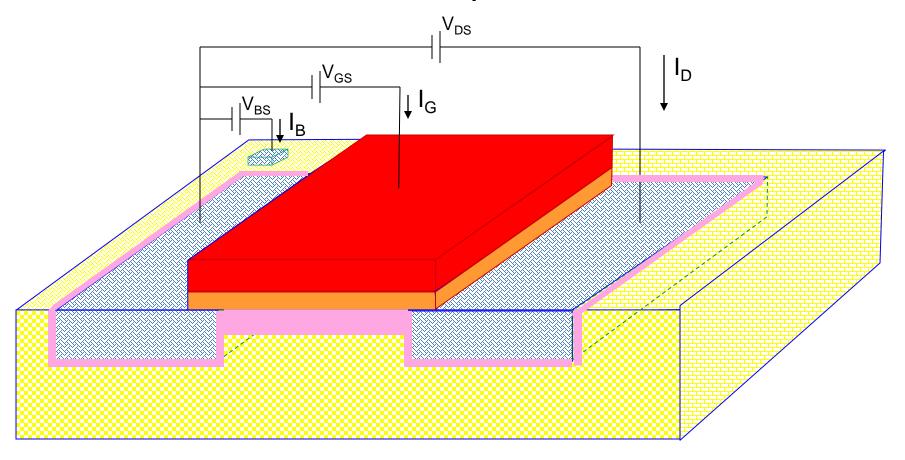

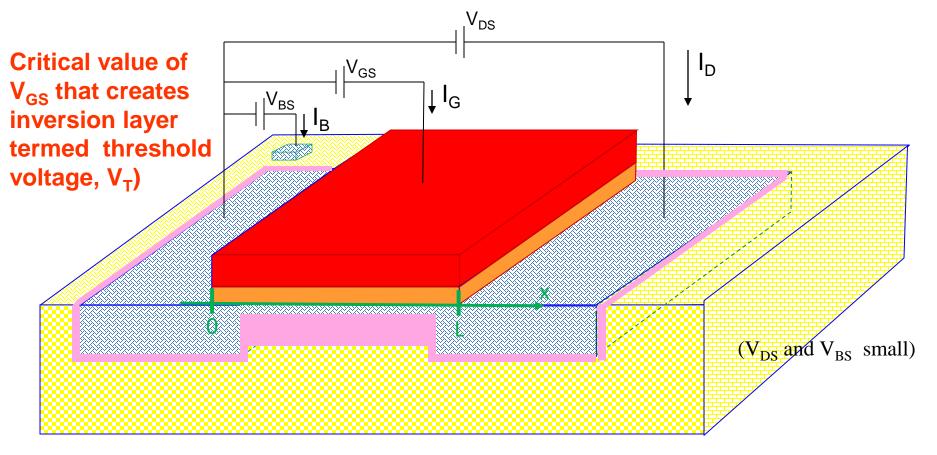

Model in Cutoff Region

Increase V<sub>GS</sub> more

Inversion layer forms in channel

Inversion layer will support current flow from D to S

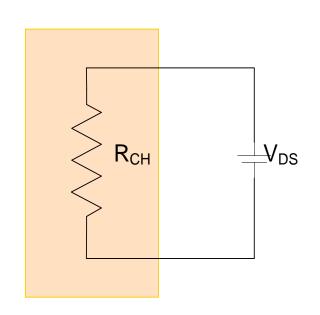

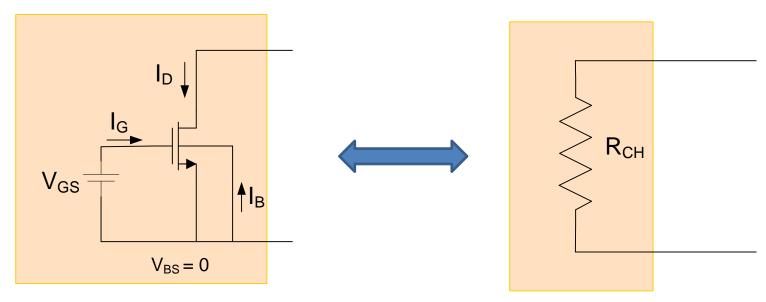

Channel behaves as thin-film resistor

$$I_DR_{CH}=V_{DS}$$

$I_G=0$

$I_B=0$

# Triode Region of Operation

For V<sub>DS</sub> small

$$R_{CH} = \frac{L}{W} \frac{1}{(V_{GS} - V_{TH}) \mu C_{OX}}$$

$$I_{D} = \mu C_{OX} \frac{W}{L} (V_{GS} - V_{TH}) V_{DS}$$

$$I_{G} = I_{B} = 0$$

Behaves as a resistor between drain and source

Model in Deep Triode Region

# Triode Region of Operation

For V<sub>DS</sub> small

$$R_{CH} = \frac{L}{W} \frac{1}{\left(V_{GS} - V_{TH}\right) \mu C_{OX}}$$

Resistor is controlled by the voltage V<sub>GS</sub> Termed a "Voltage Controlled Resistor" (VCR)

$V_{GC}(x)$  approx. constant for small  $V_{DS}$

$I_DR_{CH}=V_{DS}$   $I_G=0$  $I_B=0$

Increase  $V_{DS}$

$V_{GC}(x)$  changes with x for larger  $V_{DS}$

Inversion layer thins near drain

I<sub>D</sub> no longer linearly dependent upon V<sub>DS</sub>

Still termed "ohmic" or "triode" region of operation

$I_D = \hat{I}$

$I_{G}=0$

$I_B = 0$

# Triode Region of Operation

For V<sub>DS</sub> larger

$$R_{CH} = \frac{L}{W} \frac{1}{(V_{GS} - V_{TH}) \mu C_{OX}}$$

$$I_{D} = \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}$$

$$I_{G} = I_{B} = 0$$

Increase V<sub>DS</sub> even more

$V_{GC}(L) = V_{TH}$  when channel saturates

Inversion layer disappears near drain Termed "saturation" region of operation Saturation first occurs when  $V_{DS}=V_{GS}-V_{TH}$

$$I_D = i$$

$$I_G=0$$

$$I_B = C$$

# Saturation Region of Operation

$$I_{D} = \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}$$

For V<sub>DS</sub> at onset of saturation —

or equivalently

$$I_{D} = \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{GS} - V_{TH}}{2} \right) \left( V_{GS} - V_{TH} \right)$$

or equivalently

$$I_{D} = \frac{\mu C_{OX} W}{2L} (V_{GS} - V_{TH})^{2}$$

$$I_{G} = I_{B} = 0$$

Increase  $V_{DS}$  even more (beyond  $V_{GS}$ - $V_{TH}$ )

Nothing much changes !!

Termed "saturation" region of operation

$$I_D = ?$$

$$I_G = 0$$

$$I_B = 0$$

# Saturation Region of Operation

For V<sub>DS</sub> in Saturation

$$I_D = \frac{\mu C_{OX} W}{2L} (V_{GS} - V_{TH})^2$$

$$I_G = I_B = 0$$

**Model in Saturation Region**

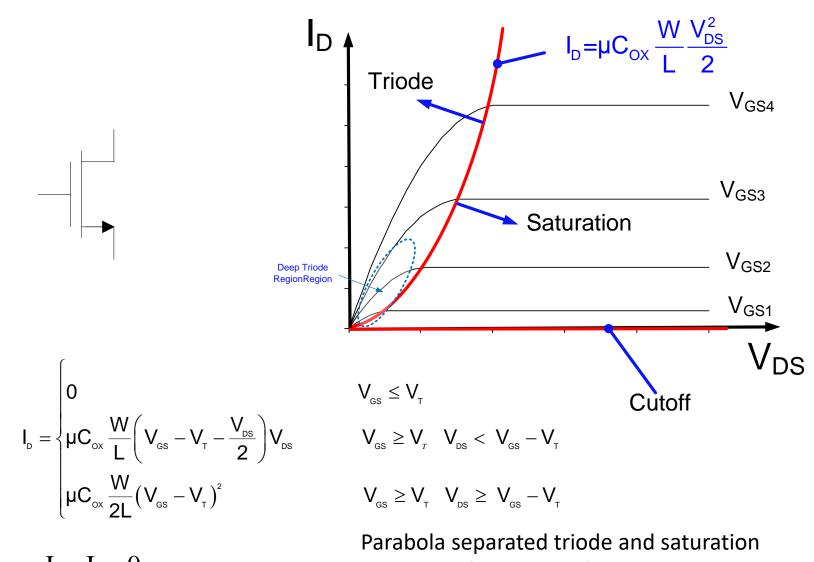

# Model Summary

n-channel MOSFET

Notation change:  $V_T = V_{TH}$ , don't confuse  $V_T$  with  $V_t = kT/q$

$$I_{D} = \begin{cases} 0 & V_{GS} \leq V_{T} \\ \mu C_{OX} \frac{W}{L} \left( V_{GS} - V_{T} - \frac{V_{DS}}{2} \right) V_{DS} & V_{GS} \geq V_{T} \quad V_{DS} < V_{GS} - V_{T} \\ \mu C_{OX} \frac{W}{2L} \left( V_{GS} - V_{T} \right)^{2} & V_{GS} \geq V_{T} \quad V_{DS} \geq V_{GS} - V_{T} \end{cases}$$

$$V_{

m GS} \leq V_{

m T}$$

Cutoff  $V_{

m GS} \geq V_{T}$   $V_{

m DS} < V_{

m GS} - V_{

m T}$  Triode

$$I_G = I_B = 0$$

Model Parameters:  $\{\mu, V_T, C_{OX}\}$  Design Parameters :  $\{W, L\}$

This is a piecewise model (not piecewise linear though)

Piecewise model is continuous at transition between regions

(Deep triode special case of triode where

$$V_{DS}$$

is small  $R_{CH} = \frac{L}{W} \frac{1}{(V_{GS} - V_T) \mu C_{OX}}$ )

Note: This is the third model we have introduced for the MOSFET

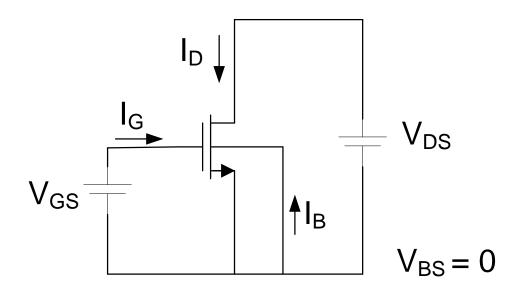

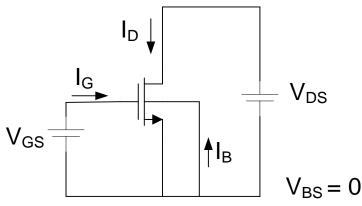

# **Model Summary**

n-channel MOSFET

Observations about this model (developed for V<sub>BS</sub>=0):

$$\begin{split} I_D &= f_1 \left( V_{GS}, V_{DS} \right) \\ I_G &= f_2 \left( V_{GS}, V_{DS} \right) \\ I_B &= f_3 \left( V_{GS}, V_{DS} \right) \end{split}$$

This is a nonlinear model characterized by the functions  $f_1$ ,  $f_2$ , and  $f_3$  where we have assumed that the port voltages  $V_{GS}$  and  $V_{DS}$  are the independent variables and the drain currents are the dependent variables

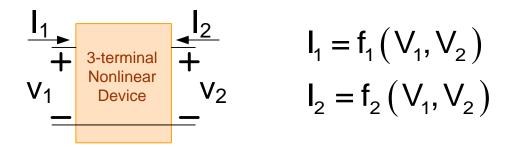

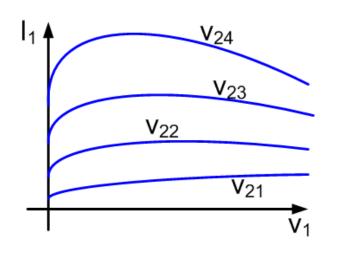

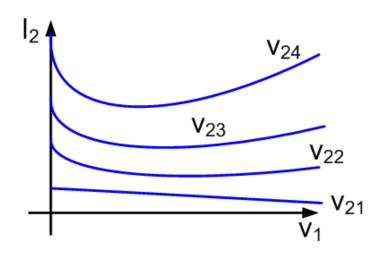

### General Nonlinear Models

I<sub>1</sub> and I<sub>2</sub> are 3-dimensional relationships which are often difficult to visualize

Two-dimensional representation of 3-dimensional relationships

## Graphical Representation of MOS Model

Parabola separated triode and saturation  $I_G = I_B = 0$ regions and corresponds to V<sub>DS</sub>=V<sub>GS</sub>-V<sub>T</sub>

Stay Safe and Stay Healthy!

# End of Lecture 16

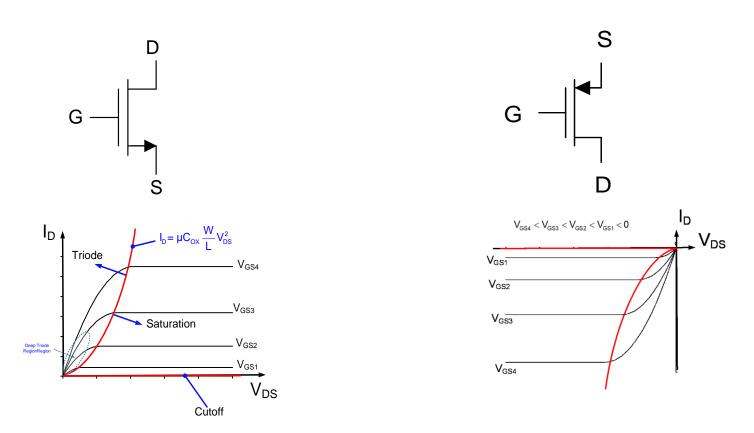

#### **PMOS** and **NMOS** Models

- Functional form identical, sign changes and parameter values different

- Will give details about p-channel model later

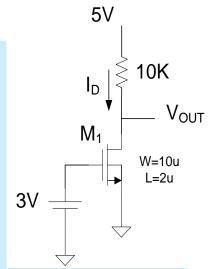

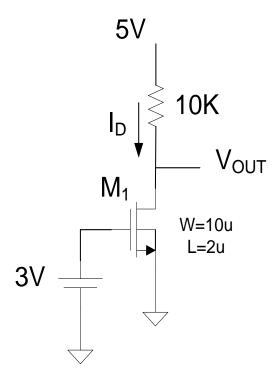

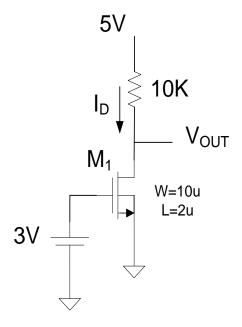

Example: Determine the output voltage for the following circuit using the square-law model of the MOSFET. Assume  $V_T$ =1V and  $\mu C_{Ox}$ =100 $\mu AV^{-2}$

#### Solution:

Since V<sub>GS</sub>>V<sub>T</sub>, M<sub>1</sub> is operating in either saturation or triode region Strategy will be to guess region of operation, solve, and then verify region Example: Determine the output voltage for the following circuit using the square-law model of the MOSFET. Assume  $V_T$ =1V and

$\mu C_{OX} = 100 \mu AV^{-2}$

#### Solution:

#### Guess M<sub>1</sub> in saturation

$$SV = I_D 10K + V_{OUT}$$

$$I_D = \frac{\mu C_{OX} W}{2L} (3 - V_T)^2$$

Required verification: V<sub>DS</sub>>V<sub>GS</sub>-V<sub>T</sub>

Can eliminate I<sub>D</sub> between these 2 equations to obtain V<sub>OUT</sub>

Example: Determine the output voltage for the following circuit using the square-law model of the MOSFET. Assume  $V_T$ =1V and  $\mu C_{Ox}$ =100 $\mu$ AV<sup>-2</sup>

Guess M<sub>1</sub> in saturation

Required verification:

$$V_{DS} > V_{GS} - V_{T}$$

$$V_{OUT} = 5V-10K \left[ \frac{100\mu AV^{-2}10\mu}{2 \cdot 2\mu} (2V)^2 \right]$$

$$V_{OUT} = -5V$$

Verification: V<sub>DS</sub>=V<sub>OUT</sub>

-5 >? 2V -- 0 No! So verification fails and Guess of region is invalid

# Example: Determine the output voltage for the following circuit using the square-law model of the MOSFET. Assume $V_T$ =1V and $\mu C_{Ox}$ =100 $\mu AV^{-2}$

Guess M₁ in triode

$$5V = I_D 10K + V_{OUT}$$

$$I_D = \frac{\mu C_{OX}W}{L} \left( 3 - V_T - \frac{V_{DS}}{2} \right) V_{DS}$$

$$V_{OUT} = 5V-10K \left[ \frac{100\mu AV^{-2}10\mu}{2\mu} \left( 2V - \frac{V_{OUT}}{2} \right) V_{OUT} \right]$$

$$V_{OUT} = 5V - \left[5\left(2V - \frac{V_{OUT}}{2}\right)V_{OUT}\right]$$

Solving for V<sub>OUT</sub>, obtain

$$V_{OUT} = 0.515V$$

Verification: V<sub>DS</sub>=V<sub>OUT</sub> 0.515 <? 2V Yes!

So verification succeeds and triode region is valid

$V_{OUT} = 0.515V$